几个月前内存制造商就已经展示了DDR4的内存,今天DDR3的继任者终于定稿了,根据JEDEC机构提供的214页的DDR4标准规范,规格简介如下:

DDR4内存每针的数据传输速度达到每秒1.6G,在原型中传输的最大速率为3.2G,鉴于目前DDR3的传输性能已经达到了1.6GT/s,未来在 DDR4的升级过程中将会进一步提升传输速度。其他的DDR4还将传输速度,而且能偶通过应用对内存进行设置。包括一个在DQ串行总线上的伪漏极开路接口,每个DQ的都附带geardown模式能够达到2,667 MT/s或以上,并采用了新的存储架构,内部整合VrefDQ并包括改善过的training模式。

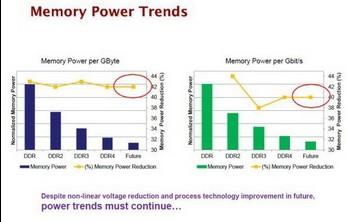

内存功耗发展趋势

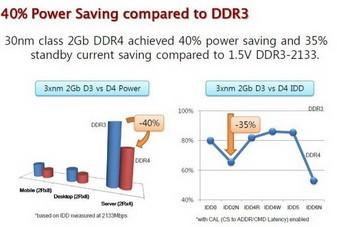

DDR4内存功耗相比DDR3降低40%。

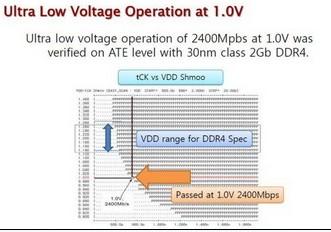

采用超低电压设计

DDR4的架构还包括一个8n的预读取的两个或者四个的存储集合,这样的设计能够保证DDR4具有高效的灵活性,将读操作和写操作两个分开,分别在两个不同的存储集合里面。同时该文件中还对内存的功耗和带宽进行了改善,尤其是在使用小颗粒的时候。

未来DDR5内存特性一览

尽管DDR4标准已经定稿,但是并不能对目前市场上的DRAM造成有效的冲击。iSuppli预计在2014年全球的占有率仅仅达到12%,而在2015年的时候这个才开始慢慢普及。